Resumen

Introducción

Overview de un procesador moderno

Lenguaje de Máquina

Convenciones de Llamado

Generación de Expresiones

Generación de Control de Flujo

Generación de Procedimientos

Linking

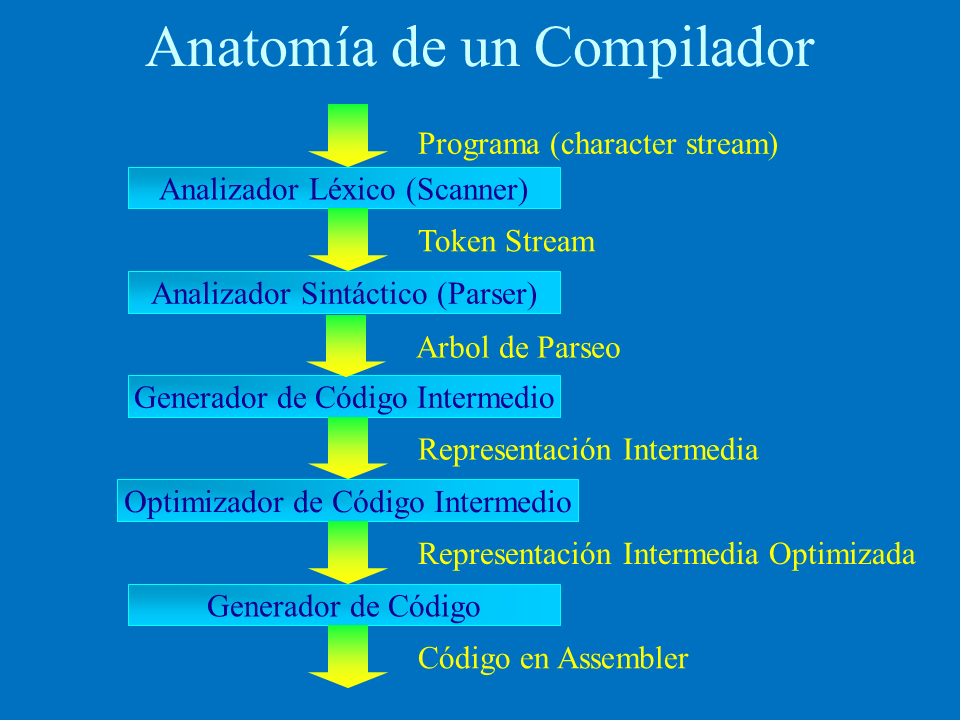

Anatomía de un Compilador

Optimizador de Código Intermedio

Generador de Código

(Gp:) Representación Intermedia Optimizada

(Gp:) Código en Assembler

Generador de Código Intermedio

(Gp:) Representación Intermedia

Analizador Léxico (Scanner)

Analizador Sintáctico (Parser)

(Gp:) Token Stream

Arbol de Parseo

(Gp:) Programa (character stream)

Anatomía de un Compilador

Generador de Código

Representación Intermedia

(Gp:) Código en Assembler

High-level IR

Analizador Léxico (Scanner)

Analizador Sintáctico (Parser)

(Gp:) Token Stream

Arbol de Parseo

(Gp:) Programa (character stream)

Low-level IR

Generador de Código Intermedio

Representación en Formato Intermedio

while (i < v.length && v[i] != 0) {

i = i+1;

}

entry

ldl i

len

<

cbr

stl i

exit

ldf v

lda

0

!=

cbr

ldf v

ldl i

ldl i

0

+

El Generador de Código debe…

Traducir todas las instrucciones en la representación intermedia a lenguaje ensamblador

Asignar espacio para variables, arreglos, etc.

Adherirse a las convenciones de llamado

Crear la información simbólica necesaria

Resumen

Introducción

Resumen de un procesador moderno

Lenguaje de Máquina

Convenciones de Llamado

Generación de Expresiones

Generación de Control de Flujo

Generación de Procedimientos

Linking

Resumen de un Procesador Moderno

ALU

Control

Memoria

Registros

Memory

Registers

ALU

Control

Arithmetic and Logic Unit

Hace la mayoría de operaciones

Con forma:OP Rdest, Rsrc1, Rsrc2

Operaciones son:

Operaciones aritméticas (add, sub, mul)

Operaciones lógicas (and, sll)

Operaciones de comparación (seq, sge, slt)

Memory

Registers

Control

ALU

Arithmetic and Logic Unit

Muchas operaciones aritméticas pueden causar una excepción

overflow y underflow

Puede operar en distintos tipos de datos

8, 16, 32 bits

Aritmética con y sin signo

Operaciones de punto flotante (ALU separada)

Instrucciones para convertir entre formatos (cvt.s.d)

Memory

Registers

Control

ALU

Control

Maneja la secuencia de Instrucciones

Ejecución de Instrucciones

Todas las instrucciones están en memoria

Fetch de la instrucción a la que apunta el PC y ejecutarla

Para instrucciones generales, incrementar el PC para que apunte a la siguiente posición de memoria

Memory

Registers

ALU

Control

Control

Saltos no condicionales

Fetch de la siguiente instrucción de una localidad diferente

Salto incondicional a una dirección dada

j label

Salto incondicional a una dirección en un registro

jr rsrc

Para manejar llamadas a procedimientos, se hace un salto incondicional, pero se guarda la siguiente dirección en la secuencia actual en un registro

jal label jalr rsrc

Memory

Registers

ALU

Control

Control

Saltos Condicionales

Ejectuamos un test,si es éxitoso, fetch de instrucciones de una nueva dirección,de otra forma fetch de la siguiente instrucción

Las instrucciones son de la forma: brelop Rsrc1, Rsrc2, label

relop es de la forma: eq, ne, gt, ge, lt, le

Memory

Registers

ALU

Control

Control

Transferencia de control en casos especiales (raros)

traps y excepciones

Mecanismo

Guardar la posición de la siguiente instrucción (o la actual)

Encontrar la dirección a la que hay que saltar (de un vector de excepciones)

Saltar a esa posición

Memory

Registers

ALU

Control

Memory

Espacio de Direcciones plano

Compuesto de words

Direccionable por bytes

Necesitamos guardar

Programa

Variables locales

Stack

Heap

Memory

Registers

ALU

Control

Página siguiente  |