EL BUS I2C

Para simplificar la interconexión de dispositivos al microprocesador, Philips desarrolló un sencillo bus bidireccional basado en dos hilos por el que se trasmiten los datos vía serie y lo llamó El Bus I2C.

EL Bus I2C (Inter- Integrated Circuits) fue desarrollado al principio de los 80’s. Su propósito original fue el de proporcionar una manera fácil de conectar un CPU a los chips periféricos en un equipo de TV.

EL PROBLEMA A RESOLVER:

Los dispositivos periféricos en sistemas embebidos se conectan al mControlador como dispositivos de E/S mapeados en memoria usando las líneas paralelas del bus de dirección y de datos. Esto produce una gran cantidad de pistas en el PCB para enrutar las líneas de direcciones y de datos, sin mencionar un número de decodificadores de direcciones y lógica adicional para conectar todo.

Muchas líneas de control implican que el sistema sea más susceptible a perturbaciones por Interferencia Electromagnética (EMI) y Descarga Electrostática (ESD).

Las características más importantes del bus I2C son:

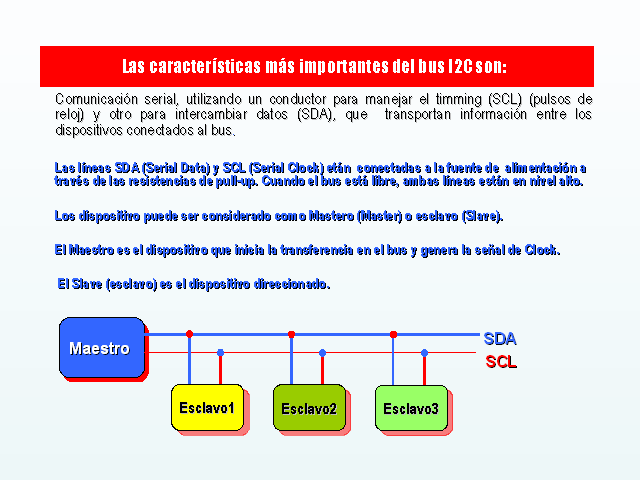

SubComunicación serial, utilizando un conductor para manejar el timming (SCL) (pulsos de reloj) y otro para intercambiar datos (SDA), que transportan información entre los dispositivos conectados al bus.

Las líneas SDA (Serial Data) y SCL (Serial Clock) etán conectadas a la fuente de alimentación a través de las resistencias de pull-up. Cuando el bus está libre, ambas líneas están en nivel alto.

Los dispositivo puede ser considerado como Mastero (Master) o esclavo (Slave).

El Maestro es el dispositivo que inicia la transferencia en el bus y genera la señal de Clock.

El Slave (esclavo) es el dispositivo direccionado.

(Gp:) Maestro

(Gp:) Esclavo1

(Gp:) Esclavo2

(Gp:) Esclavo3

(Gp:) SDA

(Gp:) SCL

Transmisión de bits

– Los bits de datos van por SDA

– Por cada bit de información es necesario un pulso de SCL

– Los datos sólo pueden cambiar cuando SCL está a nivel bajo

Los datos transitan en la bajada del reloj

El dato es recibido en el borde de bajada del reloj

El bit más significativo se envía primero

El nodo que recibe debe manejar un acknowledge (bajo en SDA) después de completado el byte

El nodo maestro siempre genera el reloj

Cada dispositivo es reconocido por una única dirección (si es un microcontrolador, LCD, memoria o teclado) y cualquiera puede operar como transmisor o receptor de datos, dependiendo de la función del dispositivo.

Un display es solo un receptor de datos mientras que una memoria recibe y transmite datos.

Las características más importantes del bus I2C son:

Sub

Trasferencia de datos:

Los datos y direcciones que se transmiten por SDA son de 8 bits.

Tras cada bloque debe recibirse una señal de reconocimiento.

.

Las características más importantes del bus I2C son:

La cantidad de dispositivos que se pueden conectar al bus está limitada, solamente, por la máxima capacidad permitida de 400 pF.

El bus permite la conexión de varios Masters, ya que incluye un detector de colisiones.

El protocolo de transferencia de datos y direcciones posibilita diseñar sistemas completamente definidos por software.

Las características más importantes del bus I2C son:

La especificación original, o modo de estandar, fue para transferencia de datos hasta 100 Kbps.

El bus serial I2C ha sido extendido para soportar velocidades de hasta 3.4 Mbits/s. Combinado con una función de desplazamiento del nivel de voltaje, en modo High-speed (Hs-mode) ofrece una solución ideal para los sistemas de tecnología mezclada, donde las altas velocidades y la variedad de voltajes (5 V, 3 V o menor) son comúnmente usados.

El reloj determina la velocidad de transmisión de los datos.

Las características más importantes del bus I2C son:

Los modos de transferencia de datos del bus I2C

Modo Estándar (S-mode) aproximadamente a 100 kBits/Seg.

Modo Rápido (F-mode) aproximadamente a 400kbits/Seg.

Modo Alta velocidad (Hs-mode) mas de 3,4 Mbits/Seg.

Las características más importantes del bus I2C son:

Definiciones o términos utilizados en relación con las funciones del bus I2C

Maestro (Master): Dispositivo que determina la temporización y la dirección del tráfico de datos en el bus. Es el único que aplica los pulsos de reloj en la línea SCL. Cuando se conectan varios dispositivos maestros a un mismo bus la configuración obtenida se denomina "multi-maestro".

Esclavo (Slave): Cualquier dispositivo conectado al bus incapaz de generar pulsos de reloj. Reciben señales de comando y de reloj proveniente del dispositivo maestro.

Bus Desocupado (Bus Free): Estado en el cual ambas líneas (SDA y SCL) están inactivas, presentando un estado lógico alto. Unicamente en este momento es cuando un dispositivo maestro puede comenzar a hacer uso del bus.

Comienzo (Start): Sucede cuando un dispositivo maestro hace ocupación del bus, generando esta condición. La línea de datos (SDA) toma un estado bajo mientras que la línea de reloj (SCL) permanece alta.

Parada (Stop): Un dispositivo maestro puede generar esta condición dejando libre el bus. La línea de datos toma un estado lógico alto mientras que la de reloj permanece también en ese estado.

Dato Válido (Valid Data): Sucede cuando un dato presente en la línea SDA es estable mientras la línea SCL está a nivel lógico alto.

Formato de Datos (Data Format): La transmisión de datos a través de este bus consta de 8 bits de datos (ó 1 byte). A cada byte le sigue un noveno pulso de reloj durante el cual el dispositivo receptor del byte debe generar un pulso de reconocimiento, conocido como ACK (del inglés Acknowledge). Esto se logra situando la línea de datos a un nivel lógico bajo mientras transcurre el noveno pulso de reloj.

Dirección (Address): Cada dispositivo diseñado para funcionar en este bus dispone de su propia y única dirección de acceso, que viene pre-establecida por el fabricante. Hay dispositivos que permiten establecer externamente parte de la dirección de acceso. Esto permite que una serie del mismo tipo de dispositivos se puedan conectar en un mismo bus sin problemas de identificación. La dirección 00 es la denominada "de acceso general", por la cual responden todos los dispositivos conectados al bus.

Lectura/Escritura (Bit R/W): Cada dispositivo dispone de una dirección de 7 bits. El octavo bit (el menos significativo ó LSB) enviado durante la operación de direccionamiento corresponde al bit que indica el tipo de operación a realizar. Si este bit es alto el dispositivo maestro lee información proveniente de un dispositivo esclavo. En cambio, si este bit fuese bajo el dispositivo maestro escribe información en un dispositivo esclavo.

Definiciones o términos utilizados en relación con las funciones del bus I2C

Terminología básica del Bus I2C

Respaldo Tecnológico:

Tanto Philips como como otros fabricantes de dispositivos compatibles con I2C disponen de una amplia gama de circuitos integrados, incluyendo memorias RAM y EEPROM, microcontroladores, puertos de E/S, codificadores DTMF, tranceptores IR, conversores A/D y D/A, relojes de tiempo real, calendarios, etc

Dado que no siempre se requiere alta velocidad de transferencia de datos este bus es ideal para sistemas donde es necesario manejar información entre muchos dispositivos y, al mismo tiempo, se requiere poco espacio y líneas de circuito impreso. Por ello es común ver dispositivos I2C en video grabadoras, sistemas de seguridad, electrónica automotriz, televisores, equipos de sonido y muchas otras aplicaciones más.

Incluso, y gracias a que el protocolo es lo suficientemente simple, usualmente se ven dispositivos I2C insertados en sistemas microcontrolados que no fueron diseñados con puertos I2C, siendo el protocolo generado por el firmware.

También hay dispositivos de adaptación que permiten conectar buses originalmente paralelos a sistemas I2C. Tal es el caso del chip PCD 8584 de Philips el cual incorpora en el chip todo lo necesario para efectuar dicha tarea.

Hay, además, circuitos integrados cuya única misión es adaptar los niveles presentes en el bus I2C y TTL, permitiendo resolver fácil y rápidamente la interconexión de dispositivos de dicha familia con el I2C.

Respaldo Tecnológico:

El protocolo del Bus I2C

Formato del Mensaje

Un protocolo orientado a BIT

Handshaking

Bidireccional

Maestro envía datos a un esclavo

Transferencia de datos:

SubEl Maestro genera la condición de Start.

Cada palabra puesta en el bus SDA debe tener 8 bits, la primera palabra transferida contiene la dirección del Esclavo seleccionado.

Tras el envío del start o inicio, en los siguientes 7 bits se codifica la dirección del dispositivo. Y el octavo bit indica si se hace lectura(1) o escritura(0).

Después de cada 8 bits, el master debe esperar una señal de reconocimiento como respuesta por parte del esclavo, lee el estado de la línea SDA, si vale 0 (impuesto por el esclavo), el proceso de transferencia continúa. Si vale 1, indica que el circuito direccionado no valida la comunicación, entonces, el Maestro genera un bit de stop para liberar el bus I2C.

Este acuse de recibo se denomina ACK (acknowledge) y es una parte importante del protocolo I2C.

Al final de la transmisión, el Maestro genera la condición de Stop y libera el bus I2C, las líneas SDA y SCL pasan a estado alto.

Inicio de transmisión

– La transmisión la inicia el maestro

– Flanco de bajada en SDA con SCL a nivel alto

– Cuando nadie accede al bus hay un nivel alto en SCL y SDA

Condiciones de START y STOP:

Una vez finalizada la comunicación se debe informar de esta situación (condición de Stop). La línea SDA pasa a nivel alto mientras SCL permanece en estado alto.

START:

la línea SDA cae a cero mientras SCL permanece en nivel alto. A partir de este momento comienza la transferencia de datos.

Start y Stop

Start –SDA baja cuando el reloj (SCL) es alto

Stop – SDA sube cuando SCL es alto

(Normalmente no hay transición cuando el reloj es alto)

(Gp:) SDA baja antes que SCL

(Gp:) SCL alta antes que SDA

Enviando a un Esclavo

Eventos del bus I2C : leyendo un Acknowledge de un Esclavo

Cuando se ha transmitido al bus un byte de dirección o de dato éste debe ser “ RECONOCIDO” por el o los esclavos.

En el caso de una dirección: Si la dirección concuerda con la propia entonces ese esclavo y solamente ese esclavo enviará un acuse de recibido de la dirección con un ACK. También se responde con un ACK en el caso de un byte transmitido a un esclavo ya direccionado . El esclavo que va a dar un ACK pone a bajo la línea SDA inmediatamente después de la recepción del octavo bit, o, en caso de un byte de dirección , inmediatamente después de la evaluación de su dirección.

Esto significa que tan pronto como el maestro baja SCL para completar la transmisión del bit (1), SDA será puesto a bajo por el esclavo (2).

El maestro ahora emite un pulso de reloj en la línea SCL (3) El esclavo liberará la línea SDA hasta la terminación de este pulso (4) de reloj.

El Bus queda disponible de nuevo para que el maestro continúe enviando datos o generar una condición de STOP.

En caso de que un dato vaya a ser escrito al esclavo, este ciclo debe completarse antes de que se genere una condición STOP. El esclavo estará bloqueando el bus (la línea SDA es mantenida en bajo por el esclavo) hasta que el maestro haya generado un pulso de reloj en la línea SCL.

Reconocimiento (Acknowledge) :

Reconocimiento

El bit de reconocimiento es obligatorio en la transferencia de datos. El pulso de reloj correspondiente al bit de reconocimiento (ACK) es generado por el Master. El Transmisor desbloquea la línea SDA ("1") durante el pulso de reconocimiento. El receptor debe poner a "0" la línea SDA durante el pulso ACK de modo que siga siendo "0" durante el tiempo que el master genera el pulso "1" de ACK.

Normalmente un receptor cuando ha sido direccionado esta obligado a generar un ACK después de que cada byte a sido recibido.

Cuando un dispositivo esclavo no genera el bit ACK (porque esta haciendo otra cosa y no puede atender el Bus) debe mantener el esclavo la línea SDA a nivel "1" durante el bit ACK. El Master entonces puede generar una condición de STOP abortando la transferencia de datos o repetir la condición de Inicio enviando una nueva transferencia de datos.

Si un Esclavo-receptor que esta direccionado no desea recibir mas bytes, el master debe detectar la situación y no enviar mas bytes. Esto se indica porque el esclavo no genera el bit ACK en el primer byte que sigue. El esclavo pone la línea SDA a "1" lo que es detectado por el Master el cual genera la condición de Stop o repite la condición de Inicio.

Si un Master-receptor esta recibiendo datos de un Esclavo-transmisor debe generar un bit ACK tras cada byte recibido de transmisor, para finalizar la transferencia de datos no debe generar el ACK tras el ultimo byte enviado por el esclavo. El esclavo-transmisor debe permitir desbloquear la línea SDA generando el master la condición de Stop o de Inicio.

Transferencia completa

RELACIÓN ENTRE LOS NIVELES DE SDA Y SCL

Todos los maestros deben generar una subida en la línea SCL (2), leer el nivel en SDA (3) y generar una caida en la línea SCL (4).

El Esclavo no debe cambiar el dato durante el tiempo que SCL es alto ( de lo contrario podría generarse una condición START o STOP imprevista) .

Durante (1) y (5), el esclavo puede cambiar el estado de la línea SDA.

En total está secuencia debe ser realizada 8 veces para completar el byte dato.

Los bytes siempre son transmitidos con el Bit Más Significativo primero.

Maestro lee datos de un esclavo

Eventos del Bus I2C : Recibiendo un byte de un Esclavo

Una vez que el esclavo ha sido direccionado y el esclavo ha reconocido ésto, el maestro puede recibir un byte del esclavo si el bit R/W en la dirección se puso en modo READ ( puesto a ‘1’)

La sintaxis del protocolo es la misma que cuando se transmite un byte a un esclavo, excepto que ahora no se le permite al maestro tocar la línea SDA. Previo al envió por la línea SCL,de los 8 pulsos de reloj necesarios para el envió del byte , el maestro libera la línea SDA. Ahora el esclavo tomará el control de esta línea. La línea se irá a alto si se desea transmitir un ‘1’ o si el esclavo desea mandar un ‘0’, se mantiene en bajo.

Para operar un esclavo sobre el Bus I2C solo son necesarios seis simples códigos, suficientes para enviar o recibir información.

Un bit de Inicio

7-bit o 10-bit de direccionamiento

Un bit R/W que define si el esclavo es transmisor o receptor

Un bit de reconocimiento

Mensaje dividido en bytes

Un bit de Stop

Las líneas SDA y SCL son del tipo drenador abierto, similares a las de colector abierto pero asociadas a un transistor de efecto de campo (ó FET)..

Se deben poner en estado alto (conectar a la alimentación por medio de resistores Pull-Up) para construir una estructura de bus tal que se permita conectar en paralelo múltiples entradas y salidas

Esquema básico de conexiones

Esquema básico de conexiones

Características de una conexión en colector abierto

– Permite conectar varias fuentes de datos a un mismo hilo

– Nivel alto en el bus

– Si ningún dispositivo accede al bus

– Si ningún dispositivo transmite un cero

– Nivel bajo en el bus

– Si un dispositivo pone un nivel bajo

– Si dos dispositivos escriben a la vez siempre prevalecen los ceros

• AND cableada

– Si un dispositivo escribe un nivel alto pero lee un cero indica que otro dispositivo está también accediendo al b

Esquema básico de conexiones

Inconvenientes de la conexión en colector abierto

– Las capacidades de la línea se cargan a través del pull-up

– Se puede solucionar utilizando una carga activa en lugar de un resistor

Esquema básico de conexiones

Las dos líneas de comunicación disponen de niveles lógicos altos cuando están inactivas. De entrada el número de dispositivos que se puede conectar al bus es ilimitado, pero las líneas tienen una especificación de capacidad de carga máxima de 400pF.

Terminación de Bus

El bus I2C

Ejemplo de una configuración del bus I2C usando dos microcontroladores

Configuración Multi-Maestro

Cuando el MCU1 emite una condición start e enviá una dirección, todos los esclavos escucharán ( incluyendo a MCU2 el cual en ese momento es considerado un esclavo también) . Si la dirección no concuerda con la dirección del CPU2, este dispositivo debe mantenerse de regreso a cualquier actividad hasta que el bus se desocupe de nuevo después de una condición stop.

As long as the two MCU's monitor what is going on on the bus (start and stop) and as long as they are aware that a transaction is going on because the last issued command was not a STOP, there is no problem.

Let's assume one of the MCU's missed the START condition and still thinks the bus is idle, or it just came out of reset and wants to start talking on the bus which could very well happen in a real-life scenario. This could lead to problems.

Protocolo multimaestro

– Con dos maestros en el bus existe posibilidad de conflicto

Arbitración: procedimiento para asegurar que sólo un maestro tiene el

control del bus en un instante

– Si un maestro está utilizando el bus no puede ser interrumpido por otro.

• Desde START hasta STOP

– Si dos maestros intentan comenzar a utilizar el bus a la vez:

• Conexión del bus en colector abierto ?? prevalecen los ceros

• A la vez que ponen datos en el bus, escuchan la línea.

• Si un maestro está intentando enviar un nivel alto y lee un nivel bajo

– Existe otro maestro utilizando el bus

– Deja de transmitir esperando que la línea quede libre (condición de STOP)

Configuración Multi-Maestro

Ejemplo de aplicaciones del Bus I2C

LECTOR DE SMARTCARDS

Conexión de una EEPROM serial y un Reloj de tiempo real, con bus I2C, para su uso en un lector de smartcards

Ejemplo de aplicaciones del Bus I2C

El bus I2C

Conexión de medidores ultrasónico de distancias a un mC Basic Stamp 2 usando el bus I2C.

El módulo SRF10 es un medidor ultrasónico de distancias miniatura para robots que representa la ultima generación en sistemas de medidas de distancias por sonar.

El sensor es capaz de detectar objetos a una distancia de 6 m con la facilidad de conectarse al microcontrolador mediante un bus I2C, por lo que se pueden conectar cuantos sensores sean necesarios en el mismo bus.

Con una alimentación unica de 5V, solo requiere 15 mA, para funcionar y 3mA mientras esta en reposo.

Ejemplo de aplicaciones del Bus I2C

El bus I2C

Para el programador, el sensor SRF10 se comporta de la misma manera que las EEPROM de las series 24xx, con la excepción de que la dirección I2C es diferente. La dirección por defecto de fábrica del sensor es 0xE0. El usuario puede cambiar esta dirección con 16 direcciones diferentes: E0, E2, E4, E6, E8, EA, EC, EE, F0, F2, F4, F6, F8, FA, FC o FE, por lo que es posible utilizar hasta 16 sensores sobre un mismo bus I2C.

Además de las direcciones anteriores, todos los sonares conectados al bus I2C responderán a la dirección 0 -al ser la dirección de atención general. Esto significa que escribir un comando de medición de la distancia para la dirección 0 de I2C (0x00) iniciará las mediciones en todos los sensores al mismo tiempo.

Ejemplo de aplicaciones del Bus I2C

Esquema del circuito para la conexión de dos sensores ultrasónicos SRF08 al controlador Basic Stamp 2

Ejemplo de aplicaciones del Bus I2C

Dispositivos I2C con el PICAXE

WRITEI2C

Sintáxis: WRITEI2Clocation,(variable,…)

– Location es una variable /constante que especifica la dirección de un byte o palabra

– Variable(s) contiene el byte(s) de dato que se va a escribir

Función:

Escribe a la localidad I2C el contenido de la variable(s).

READI2C

Sintáxis: READI2C location,(variable,…)

– Location es una variable /constante que especifica la dirección de un byte o palabra

– Variable(s) recibe el byte(s) leido(s).

Funcción:

Lee la localidad I2C contenida en la(s) variable(s).

I2CSLAVE

Sintáxis: I2CSLAVE slave, speed, address

– Slave es la dirección i2c del esclavo

– Speed es la palabra i2cfast (400kHz) o i2cslow (100kHz) a 4Mhz

Address es la palabra i2cbyte o i2cword

Función:

El comando i2cslave es usado para configurar las terminales PICAXE para usar el I2C y para definir el tipo de dispositivo I2C a ser direccionado

Instrucciones en Basic del PICAXE par usar el bus I2C