13

Controladores de entrada/salida

El principal objetivo de un controlador de E/S es establecer una abstracción

Simplificar la visión que el computador tiene de los periféricos

Ocultar detalles físicos, de formato, de temporización…

Procesador

control

dirección

dato

Memoria

controlador E/S

controlador E/S

periférico

periférico

…

14

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

15

Funciones de un controlador

Control y temporización: coordinar el tráfico entre los recursos internos y los dispositivos externos

procesador

periférico

controlador

solicitud

solicitud

reconocimiento

reconocimiento

reconocimiento

reconocimiento

dato

dato

Ejemplo: transferencia de datos de un dispositivo al procesador

16

Funciones de un controlador

Almacenamiento temporal de datos: compensar la diferencia de velocidad en las transferencias

Si los datos llegan con demasiada rapidez se almacenan y se van procesando al ritmo adecuado

Si los datos llegan con demasiada lentitud se van almacenando y se procesan cuando hay suficientes

Detección de errores

Defectos mecánicos o eléctricos

Errores de transmisión

17

Funciones de un controlador

Comunicación con el procesador

Decodificar órdenes provenientes del procesador

Intercambiar datos

Comunicar información de estado y condiciones de error

Reconocimiento de una dirección como correspondiente a uno de los periféricos bajo control

Comunicación con el dispositivo: intercambio de señales de control, estado y datos

18

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

19

Interconexión con los controladores

Desde el punto de vista del procesador, la entrada/salida funciona igual que la memoria

Operaciones de lectura

Operaciones de escritura

Un controlador de E/S tiene dos interfaces

Con el procesador y la memoria

Con los periféricos

20

Interconexión con los controladores

Las conexiones entre el procesador, la memoria y los controladores E/S reciben usualmente el nombre de bus

Líneas de control

Líneas de dirección

Líneas de datos

21

Estructura de un controlador de E/S

Registro de datos

Almacena los datos que se envían/reciben

22

Estructura de un controlador de E/S

Registro de estado

Proporciona información del estado actual

Puede funcionar como un registro de control para almacenar la información de control transmitida por el procesador

23

Estructura de un controlador de E/S

Lógica de entrada/salida

Interactúa con el procesador por medio de líneas de control por las que recibe órdenes del procesador pero que también puede usar para solicitar recursos (acceso al bus…)

Reconoce y genera los identificadores asociados con cada dispositivo que controla

24

Estructura de un controlador de E/S

Lógica específica de interfaz con cada dispositivo gestionado

25

Estructura de un periférico

Lógica de control: maneja el periférico en función de las indicaciones del controlador de E/S

26

Estructura de un periférico

Transductor: convierte señales digitales a otra forma de energía (salida) o viceversa (entrada)

Un buffer permite el almacenamiento temporal de las señales

Hay gran variedad de interfaces entre el periférico y el exterior (teclado, monitor, ratón…)

27

Interfaz controlador de E/S – periférico

La interfaz puede ser serie o paralela

Serie: solo hay una línea de conexión, los bits se transmiten de uno en uno

Paralela: hay varias líneas de conexión, lo que permite transmitir varios bits de forma simultánea

Tradicionalmente se asocian las interfaces paralelas con dispositivos de alta velocidad (cinta, disco…) y las interfaces serie con dispositivos más lentos (impresoras, terminales…)

Hoy en día, las interfaces serie de alta velocidad hacen que las paralelas sean cada vez menos frecuentes

28

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

29

Técnicas para las operaciones de E/S

E/S programada

Los datos se intercambian entre el procesador y el controlador

El procesador envía una orden y espera a que la operación termine ejecutando un programa que controla la operación (lectura, escritura, comprobación de estado…)

30

Técnicas para las operaciones de E/S

Desventajas de la E/S programada

Consume tiempo: el procesador debe dedicar parte de su tiempo a gestionar las operaciones de E/S

Mantiene al procesador innecesariamente ocupado: si el procesador es más rápido se verá obligado a comprobar el estado del controlador una y otra vez hasta que la operación finaliza

Velocidad limitada: la velocidad de transferencia está limitada por la velocidad a la que el procesador puede atender al controlador

31

Técnicas para las operaciones de E/S

E/S mediante interrupciones

El procesador da la orden y sigue ejecutando otras instrucciones hasta que el controlador de E/S le interrumpe para comunicarle que la operación ha concluido

Es más eficiente porque elimina esperas innecesarias, pero los datos siguen pasando a través del procesador

Consume tiempo

Limita velocidad

32

Técnicas para las operaciones de E/S

Acceso directo a memoria (DMA – Direct Memory Access)

La memoria y el controlador de E/S intercambian datos directamente sin intervención del procesador

El procesador da la orden y sigue ejecutando otras instrucciones hasta que el controlador de E/S le interrumpe para comunicarle que la operación ha concluido, pero los datos no pasan a través de él

33

Técnicas para las operaciones de E/S

La E/S programada puede resultar más rápida para pequeñas cantidades de datos, pero el procesador no podrá hacer nada más

La E/S mediante interrupciones libera el procesador para que haga otras tareas, pero la transferencia será más lenta

DMA es la técnica más eficiente cuando se trata de transmitir grandes volúmenes de información

34

Técnicas para las operaciones de E/S

Ejemplo: lectura de datos (transferencia E/S ? memoria)

35

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

36

E/S programada

Al encontrar una instrucción E/S, el procesador genera:

El identificador del controlador y el periférico

Una orden de E/S

La orden de E/S es enviada al controlador

El controlador realiza la operación y ajusta el valor del registro de estado, pero no avisa al procesador

El procesador debe controlar periódicamente el estado del controlador hasta que comprueba que la operación ha finalizado

37

Órdenes de E/S

Hay cuatro tipos de órdenes de E/S

Control: son específicas de cada tipo particular de periférico (activar periférico, indicarle que hacer…)

Test: comprueban condiciones de estado (¿conectado?, ¿disponible?, ¿operación terminada?, ¿error?…)

Lectura

El controlador lee un dato del periférico y lo almacena internamente

El procesador podrá obtener el dato pidiendo al controlador que lo ponga en el bus

Escritura

El controlador toma un dato del bus

El dato es transmitido al periférico

38

Direccionamiento de los periféricos

Las instrucciones de E/S suelen tener una correspondencia directa 1-1 con las órdenes de E/S

El formato de las instrucciones de E/S depende de la forma de direccionamiento de los dispositivos, pues deben contener la dirección adecuada

Si el procesador, la memoria y la E/S comparten un bus se pueden usar dos modos de direccionamiento

E/S asignada en memoria

E/S aislada de memoria

39

E/S asignada en memoria

Existe un único espacio de direcciones para posiciones de memoria y dispositivos de E/S

Los registros de estado y de datos de los controladores son vistos por el procesador como posiciones de memoria y accede a ellos como si lo fueran

Sólo existe una línea de lectura y una línea de escritura

Por ejemplo, con 10 líneas de dirección tendríamos un total de 210 = 1024 posiciones de memoria y E/S

40

E/S aislada de memoria

Existen líneas de lectura/escritura en memoria y otras separadas para las órdenes de E/S

Por ejemplo, con 10 líneas para memoria y otras 10 líneas de dirección para E/S tendríamos 210 = 1024 posiciones de memoria y otras tantas de E/S

Las instrucciones deben especificar si se refieren a una posición de memoria o a un dispositivo de E/S

41

E/S asignada vs. aislada

E/S asignada en memoria

La programación es más eficiente porque existe una gran variedad de instrucciones de lectura/escritura en memoria

La desventaja es que hay que compartir el valioso espacio de direcciones de memoria

E/S aislada de memoria

Hay menos opciones de programación porque sólo se dispone de unas pocas instrucciones de E/S

No se comparte el espacio de direcciones

Ambas se utilizan frecuentemente hoy en día

42

E/S asignada vs. aislada

Ejemplo de programa que realiza una operación de E/S (se asumen direcciones de 10 bits)

43

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

44

E/S mediante interrupciones

Desde el punto de vista del controlador de E/S

El controlador recibe una orden del procesador

El controlador gestiona la operación con el periférico asociado

Una vez concluye la operación, el controlador envía una interrupción al procesador

El controlador espera a que el procesador actúe

Lectura: toma el dato

Escritura: comprueba el estado

El controlador queda preparado para la siguiente operación

45

E/S mediante interrupciones

Desde el punto de vista del procesador

El procesador envía una orden al controlador y luego continúa ejecutando instrucciones

Del mismo programa si es posible paralelizar

De un programa distinto

46

E/S mediante interrupciones

Desde el punto de vista del procesador

En cada ciclo de instrucción, el procesador comprueba el estado de las interrupciones

Una vez detectada, la interrupción es procesada

47

Procesamiento de interrupciones

El procesamiento de una interrupción consiste en

Suspender la ejecución del programa y guardar su contexto

Carga la rutina de gestión de la interrupción

Puede haber una por interrupción o una por interrupción y dispositivo

Puede haber más de una adecuada

La interrupción puede haber indicado cual era la adecuada

Puede ser necesario interrogar al dispositivo al respecto

Ejecutar la rutina de gestión de la interrupción, lo que puede implicar comunicarse de nuevo con el dispositivo

Recuperar el contexto del programa anterior (u otro distinto)

48

Procesamiento de interrupciones

Procedimiento de interrupción simplificado PC = Program Counter PSW = Program Status Word

49

Procesamiento de interrupciones

El contexto de un programa se almacena en la pila del sistema

50

Procesamiento de interrupciones

Es posible que se produzca una interrupción mientras se está procesando otra

Para tratar con estos casos hay dos alternativas

Deshabilitar interrupciones

Establecer prioridades

51

Deshabilitar interrupciones

Mientras se está tratando una interrupción se ignora cualquier interrupción que llegue posteriormente

Las interrupciones posteriores quedan pendientes y se procesarán cuando acabe la actual

Las interrupciones son tratadas en un orden estrictamente secuencial, pero no se tienen en cuenta la prioridad relativa o las operaciones en tiempo crítico

52

Interrupciones con prioridades

Se permite que una interrupción de mayor prioridad interrumpa al gestor de una interrupción de menor prioridad

53

¿Quién interrumpe?

La presencia de múltiples controladores implica que es necesario establecer una estrategia para que el procesador sepa quien generó una interrupción

Múltiples líneas de interrupción

Se podrían tener varias líneas de interrupción entre el procesador y los controladores

No resulta práctico tener sino unas pocas líneas

Incluso si hay varias líneas, tendrán que ser compartidas entre controladores distintos

54

¿Quién interrumpe?

Consulta software (software poll)

Cuando se detecta una interrupción se salta a una rutina general de servicio de interrupción que consulta a cada controlador para determinar el responsable

Activar una señal de control para que el controlador responda

Direccionar el registro de estado de cada controlador

Una vez identificado el controlador se salta a una rutina específica de servicio de interrupción

El principal problema de esta técnica es que consume demasiado tiempo

55

¿Quién interrumpe?

Conexión en cadena (daisy chain)

Todos los controladores comparte una línea común para solicitar interrupciones

La línea de reconocimiento de interrupciones se conecta encadenando los controladores uno tras otro

Cuando el procesador detecta una interrupción activa el reconocimiento, que se va propagando hasta el controlador correcto

El controlador responde poniendo en el bus un identificador (vector) que el procesador usa como puntero a la rutina de interrupción

De esta forma se evita ejecutar una rutina de servicio general primero pues la consulta es hardware (hardware poll)

Esta técnica también recibe el nombre de “interrupciones vectorizadas”

56

¿Quién interrumpe?

Arbitraje de bus

Un controlador debe disponer del bus antes de poder activar una interrupción

Sólo un controlador puede interrumpir en cada momento

Cuando el procesador detecta la interrupción responde activando la línea de reconocimiento, con lo que el controlador coloca su vector en el bus (esta técnica también es vectorizada)

57

¿Quién tiene prioridad?

Las técnicas anteriores proporcionan una forma de asignar prioridades a las interrupciones

Múltiples líneas de interrupción: el procesador elige la línea que tenga mayor prioridad

Consulta software: la prioridad viene determinada por el orden en el que se consultan los controladores

Conexión en cadena: la prioridad viene determinada por el orden en el que los controladores se conectan en la cadena

Arbitraje de bus: la prioridad en la asignación del bus determina la prioridad de las interrupciones

58

Intel 82C59A

El controlador de interrupciones Intel 82C59A es un árbitro de interrupciones externo utilizado con el procesador 80386

El 80386 tiene una única línea de petición de interrupción: INTR (interrupt request)

El 80386 tiene una única línea de reconocimiento de interrupción: INTA (interrupt acknowledge)

La conexión con el 82C59A permite al procesador manejar cierta variedad de dispositivos y estructuras de prioridad

59

Intel 82C59A

Este chip se encarga únicamente de la gestión de interrupciones

Acepta solicitudes de los controladores

Determina quién tiene la prioridad más alta

Activa INTR para indicárselo al procesador

El procesador activa INTA para reconocer la solicitud

El chip pone el vector apropiado en el bus

El procesador inicia el gestor de la interrupción y pasa a comunicarse directamente con el controlador a partir de ese momento

60

Intel 82C59A

Un chip puede manejar hasta 8 controladores

Pueden conectarse varios chips en cascada para manejar hasta 64 controladores

61

Intel 82C59A

El 82C59A es programable

El procesador determina el esquema de prioridad que se va a usar cargando una palabra de control en el chip

Completamente anidado: las solicitudes de interrupción se ordenan según el nivel de prioridad (de IR0 a IR7)

Rotatorio: hay varios dispositivos con igual prioridad pero, después de ser atendido, un dispositivo pasa a tener la menor prioridad del grupo

Con máscara especial: se permite que el procesador pueda inhibir selectivamente las interrupciones desde ciertos dispositivos

62

Intel 82C55A

Mientras que el 82C59A era un árbitro de interrupciones externo, la interfaz programable de periféricos 82C55A es un verdadero controlador de E/S

Es un controlador de propósito general que puede usarse tanto para E/S programada como para E/S mediante interrupciones

Está integrado en un solo chip con 40 terminales

También se utiliza junto con el procesador 80386

63

Intel 82C55A

La interfaz externa se compone de 24 líneas de E/S configurables mediante un registro de control

Tres buses de 8 bits (A, B y C)

Dos buses de 8 bits (A y B) y cuatro bits de señales de control y estado para cada uno (CA y CB)

64

Intel 82C55A

La interfaz externa se compone de 24 líneas de E/S configurables mediante un registro de control

Cada puerto puede designarse como de entrada o salida

Las líneas C pueden usarse para sincronización mediante confirmación de señales o para petición de interrupciones

65

Intel 82C55A

La interfaz interna se compone de

Un bus bidireccional de 8 bits (D) usado para transferir datos a/desde los puertos de E/S y al registro de control

Dos líneas de dirección (A0,A1) para especificar uno de los puertos de E/S o el registro de control

66

Intel 82C55A

La interfaz interna se compone de

Una señal RESET para inicializar el controlador

Una señal CHIP SELECT que indicará el comienzo de una transferencia cuando se active junto con la señal READ o la señal WRITE

67

Procesamiento de interrupciones

Ejemplo: controlar una terminal con teclado y pantalla

68

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

69

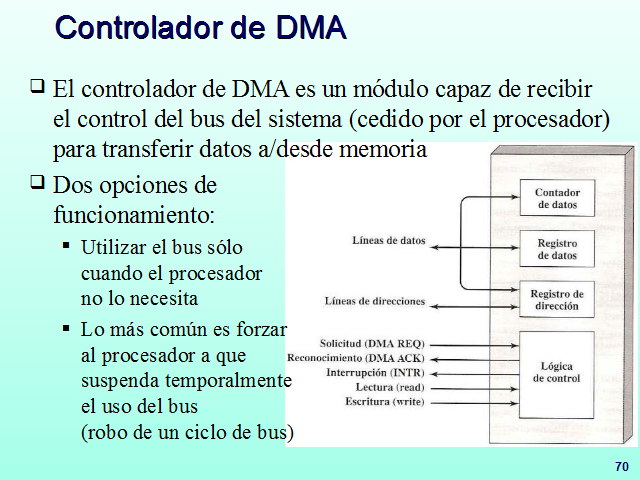

Controlador de DMA

El controlador de DMA es un módulo capaz de recibir el control del bus del sistema (cedido por el procesador) para transferir datos a/desde memoria

Dos opciones de funcionamiento:

Utilizar el bus sólo cuando el procesador no lo necesita

Lo más común es forzar al procesador a que suspenda temporalmente el uso del bus (robo de un ciclo de bus)

70

Controlador de DMA

Cuando el procesador desea leer/escribir un bloque de datos envía una orden al controlador de DMA incluyendo la siguiente información:

Indicación de si es lectura o escritura usando la línea de control apropiada

Dirección del dispositivo de E/S usando las líneas de datos

71

Controlador de DMA

Cuando el procesador desea leer/escribir un bloque de datos envía una orden al controlador de DMA incluyendo la siguiente información:

Posición inicial de memoria a la que leer/escribir usando las líneas de datos y que será almacenada en el registro de direcciones

Número de palabras a leer/escribir usando las líneas de datos y que será almacenado en el registro de cuenta de datos

72

Controlador de DMA

El controlador de DMA puede robarle el bus al procesador justo antes de que lo necesite

No es una interrupción: el procesador no guarda el contexto, tan solo espera un ciclo de bus

El procesador se ralentiza, pero para transmitir varias palabras es más eficiente que las otras dos técnicas

Cuando termina la transmisión, el controlador de DMA devuelve el control del bus al procesador

73

Controlador de DMA

El procesador puede continuar con su trabajo después de enviar la orden al controlador de DMA pues, a todos los efectos, ha delegado en él la operación

El controlador de DMA se encarga de transferir el bloque completo de datos, palabra a palabra, directamente a/desde memoria (sin pasar por el procesador)

Cuando la operación concluye, el controlador envía una interrupción al procesador para comunicárselo

74

Configuración del DMA

La configuración más económica es que todos los controladores compartan el bus del sistema

El controlador de DMA actuará como un procesador suplementario que usa E/S programada para transferir datos entre la memoria y un controlador de E/S

Es ineficiente porque cada dato consumirá dos ciclos de bus (E/S ?? DMA ?? Memoria)

75

Configuración del DMA

Integrar las funciones de DMA y E/S reduciría el número de ciclos de bus necesarios

Existe un camino entre el controlador de DMA y uno o varios controladores de E/S que no pasa por el bus del sistema

El controlador de DMA puede ser un módulo separado que gestiona varios controladores de E/S o parte de uno de ellos

Cada dato consumirá un solo ciclo del bus del sistema (DMA ?? Memoria)

76

Configuración del DMA

Se puede dar un paso más conectando los controladores de E/S a un controlador de DMA usando un bus de E/S

El controlador de DMA sólo tiene una interfaz con la E/S, dando lugar a una configuración fácilmente ampliable

De nuevo, cada dato consumirá un solo ciclo del bus del sistema (DMA ?? Memoria)

77

Intel 8237A

El controlador de DMA Intel 8237A proporciona la interfaz necesaria para realizar el acceso directo a memoria en computadores basados en procesadores de la familia 80×86

78

Intel 8237A

El 8237A es un controlador de DMA al vuelo (fly-by DMA) porque los datos no pasan nunca a través del propio controlador y no se almacenan en él

Puede controlar transferencias Memoria ?? E/S

No puede controlar transferencias E/S ?? E/S

Puede controlar transferencias Memoria ?? Memoria usando un registro temporal

En cualquier caso, mientras el controlador de DMA utiliza los buses, el procesador permanece ocioso (idle)

79

Intel 8237A – Ejemplo de transferencia

Por ejemplo, supongamos que el controlador de DMA va a transferir un bloque de datos desde la memoria hasta el disco

El controlador de disco solicitará el DMA activando la señal DREQ (DMA Request)

El controlador DMA necesita usar los buses para la transferencia (datos, dirección y control), por lo que envía al procesador la señal HRQ (Hold Request); esta señal debe estar activa durante toda la transmisión

El procesador terminará el ciclo de bus en el que se encuentre, aunque no necesariamente terminará la ejecución de la instrucción

80

Intel 8237A – Ejemplo de transferencia

Por ejemplo, supongamos que el controlador de DMA va a transferir un bloque de datos desde la memoria hasta el disco

El procesador responde al controlador de DMA activando la señal de reconocimiento HLDA (Hold Acknowledge) para indicarle que puede usar los buses

El controlador de DMA activará la señal DACK (DMA Acknowledge) para indicar al periférico que comienza la transmisión

Se realiza la transmisión de datos

Una vez finalizado el proceso, el controlador de DMA desactiva la señal HRQ para indicarle al procesador que puede volver a hacer uso de los buses

81

Intel 8237A – Ejemplo de transferencia

Cuando la transmisión de datos (paso 6) sea una lectura de memoria, el controlador de DMA realizará las siguientes operaciones:

Poner en el bus de direcciones la dirección del primer byte a leer de memoria

Activar MEMR (Memory Read) para obtener el byte de datos de memoria y ponerlo en el bus de datos

Activar IOW (Input/Output Write) para escribir en el periférico el dato presente en el bus

Decrementar el contador de bytes leídos

Incrementar el puntero a la posición que debe leerse

Repetir el proceso hasta que todos los datos se hayan leído

82

Intel 8237A – Ejemplo de transferencia

Cuando la transmisión de datos (paso 6) sea una escritura en memoria, el controlador de DMA realizará las siguientes operaciónes:

Poner en el bus de direcciones la dirección de la primera posición de memoria a escribir

Activar IOR (Input/Output Read) para obtener un byte de datos del periférico y ponerlo en el bus de datos

Activar MEMW (Memory Write) para escribir en memoria el dato presente en el bus

Decrementar el contador de bytes escritos

Incrementar el puntero a la posición en que se debe escribir

Repetir el proceso hasta que todos los datos se hayan escrito

83

Intel 8237A – Canales de DMA

El 8237A tiene cuatro canales (0, 1, 2 y 3)

Cada canal se puede programar independientemente

Cualquiera canal puede estar activo en un momento dado, incluso varios (o todos) de forma simultánea

El 8237A dispone de ocho registros de datos que utiliza para indicar la posición y el tamaño de la zona de memoria afectada por una transferencia

Un registro de dirección de memoria por cada canal

Un registro contador por cada canal

84

Intel 8237A – Canales de DMA

El 8237A dispone de cinco registros de control que se utilizan para programar y controlar la operación DMA de cada uno de los cuatro canales

Orden (command)

Estado (status)

Modo (mode)

Máscara simple (single mask)

Máscara completa (all mask)

85

Intel 8237A – Registros de Control

86

Intel 8237A – Registros de Control

Orden (command): el procesador carga este registro para controlar la operación de DMA

D0 habilita una transferencia Memoria ?? Memoria que usa el canal 0 para leer un byte en un registro temporal y el canal 1 para transferirlo de nuevo a memoria

D1 permite deshabilitar el incremento/decremento en el canal 0 para forzar la transmisión de un valor fijo

D2 habilita/deshabilita las operaciones de DMA

D3 reduce el periodo de bus

D4 elige entre prioridad fija y prioridad máxima rotatoria

D5 define el comportamiento de la señal MEMW

D6 y D7 define cuando DREQ y DACK están activas (0 ó 1)

87

Intel 8237A – Registros de Control

Estado (status): el procesador lee este registro para determinar el estado del controlador de DMA

D0 – D3: indican si los canales 0 – 3 han alcanzado el valor final de la cuenta

D4 – D7: indican si hay una petición de DMA pendiente en los canales 0 – 3

88

Intel 8237A – Registros de Control

Modo (mode): el procesador carga este registro para establecer el modo de operación de un canal

D0,D1: selecciona el canal

D2 – D7: establece el modo de operación del canal elegido

D2,D3: indican si la transferencia es E/S ? Memoria (escritura) o Memoria ? E/S (lectura)

D4: vuelve a cargar el registro de dirección de memoria y el registro contador a los valores iniciales una vez que termina la transferencia

D5: indica si durante la transferencia hay que incrementar o decrementar las direcciones

D6,D7: determina el modo de utilización del 8237A

Simple: se transfiere un único bit de datos

Bloque/Demanda: transfiere bloques (demanda = finalización prematura)

Modo cascada: permite encadenar varios para tener más de cuatro canales

89

Intel 8237A – Registros de Control

Máscara simple (single mask): el procesador modifica este registro para deshabilitar un canal determinado enmascarando la entrada DREQ

D0,D1: selecciona el canal

D2: activa o desactiva el bit de máscara correspondiente al canal seleccionado

Máscara completa (all mask): es similar al anterior pero permite habilitar/deshabilitar todos los canales en una sola operación

90

Estructura del tema

Introducción

La entrada/salida en el procesador

Definición de periférico e interfaz

Controladores de entrada/salida

Funciones de un controlador

Estructura de un controlador

Técnicas para las operaciones de entrada/salida

Entrada/salida programada

Entrada/salida mediante interrupciones

Acceso directo a memoria

Evolución de la entrada/salida

91

Evolución de la Entrada/Salida

A medida que los computadores evolucionaban, la entrada/salida ha evolucionado con ellos

El procesador controlaba directamente los periféricos

Aparece el controlador de E/S y el procesador se independiza de los detalles específicos de la de la interfaz de los periféricos; las operaciones se gestionan por medio de E/S programada

Surge el concepto de interrupción; el procesador ya no tiene que esperar por las operaciones de E/S, aumentando su eficiencia

Aparece el DMA; el procesador ya sólo necesita involucrarse al comienzo y al final de las operaciones

92

Evolución de la Entrada/Salida

A medida que los computadores evolucionaban, la entrada/salida ha evolucionado con ellos

Canales de E/S: los controladores mejoran tanto que se comportan como pequeños procesadores con su propio repertorio de instrucciones especializado

El procesador especifica al canal una secuencia de actividades, indicándole que ejecute su propio programa desde memoria, y se desentiende hasta que la secuencia termine y reciba una interrupción

Procesadores de E/S: el canal de E/S tiene memoria propia puede controlar un conjunto grande de dispositivos de E/S con una intervención mínima por parte del procesador

93

Canales de Entrada/Salida

En general, esta evolución se caracteriza por que cada vez más funciones se realizan sin intervención del procesador, mejorando con ello su rendimiento

Los canales y procesadores de E/S son un cambio importante en el concepto de controlador de E/S

Amplían el concepto de DMA con la capacidad de ejecutar programas de E/S

La capacidad de ejecutar instrucciones de E/S les proporciona completo control sobre las operaciones de E/S

Tanto el término canal como el término procesador se pueden utilizar indistintamente, pero usaremos “canal de E/S” para generalizar y evitar confusiones

94

Canales de Entrada/Salida

El procesador no ejecuta instrucciones de E/S

Se almacenan en memoria como programas independientes

Al principio de una transferencia, el procesador indica al canal de E/S qué programa debe ejecutar

El programa de entrada salida determina

Dispositivo/s a utilizar

Área/s de memoria

Prioridades

Acciones a realizar en caso de error

…

El canal de E/S sigue estas instrucciones y controla la transferencia

95

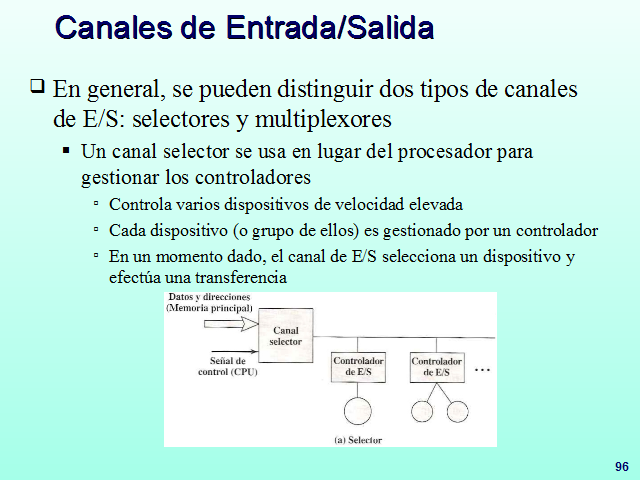

Canales de Entrada/Salida

En general, se pueden distinguir dos tipos de canales de E/S: selectores y multiplexores

Un canal selector se usa en lugar del procesador para gestionar los controladores

Controla varios dispositivos de velocidad elevada

Cada dispositivo (o grupo de ellos) es gestionado por un controlador

En un momento dado, el canal de E/S selecciona un dispositivo y efectúa una transferencia

96

Canales de Entrada/Salida

En general, se pueden distinguir dos tipos de canales de E/S: selectores y multiplexores

Un canal multiplexor puede gestionar la E/S de varios dispositivos al mismo tiempo

Los datos enviados por varios dispositivos son entrelazados y transmitidos tan rápidamente como sea posible

Dispositivos de velocidad reducida: entrelazado a nivel de bytes

Dispositivos de velocidad elevada: entrelazado a nivel de bloques

97

Bibliografía

[PATTERSON]

Estructura y diseño de computadores

interficie circuitería/programación

David A. Patterson y John L. Hennessy

Editorial Reverté, 2000

[STALLINGS]

Organización y arquitectura de computadores

William Stallings

Pearson Education – Prentice Hall, 2005 (7ª edición)

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |