ARQUITECTURA MISD

Procesadores sistólicos.

Cada unidad de proceso realiza una operación sobre los datos.

Los datos pasan por todas o parte de la unidades de proceso hasta que se ha completado el algoritmo.

Pipelined SIMD.

No muy utilizados.

13

Imagen de Hwang, 1993

SISD VS SIMD

14

Imagen de Ars Tecnica, 2006

ARQUITECTURA MIMD

Es el modelo de máquina más general y versátil.

Hay dos grandes tipos de máquinas:

Procesadores MIMD con memoria compartida:

Multiprocesadores (comparten el mismo espacio de direcciones de memoria).

Fuertemente acoplados.

Procesadores MIMD con memoria no compartida:

Multicomputadores (paso de mensajes).

Acoplamiento débil.

15

MULTIPROCESADORES

16

Pueden tener diferentes tipos de estructuras dependiendo de como estén organizadas los accesos a las diferentes memorias que constituyen la memoria de la máquina.

Tipos:

UMA (Uniform Memory Access).

NUMA (Non Uniform Memory Access).

COMA (Cache Only Memory Access).

MULTIPROCESADORES: MODELO UMA (UNIFORM MEMORY ACCESS)

El tiempo de acceso a cualquiera de las memorias es el mismo.

17

P – Procesador

MC – Memoria Compartida

Imagen de Hwang, 1993

MULTIPROCESADORES: NUMA (NON UNIFORM MEMORY ACCESS)

El tiempo de acceso a las memorias NO es el mismo

Las memorias locales son de acceso más rápido, puede haber memorias globales,

18

P – Procesador

ML – Memoria local

Imagen de Hwang, 1993

MULTIPROCESADORES: MODELO NUMA

Pueden estructurarse en clusters de máquinas.

19

P – Procesador

GSM – Global Shared Memory

CSM – Cluster Shared Memory

GIN – Global Interconnection Network

Imagen de Hwang, 1993

MULTIPROCESADORES: COMA (CACHE ONLY MEMORY ACCESS)

En los modelos UMA y NUMA aparece el problema de coherencia de caches.

El modelo COMA deriva de los protocolos de coherencia de caches.

No existe una memoria física lineal propiamente dicha sino sólo las caches y los protocolos para localizar toda la información.

20

P – Procesador

C – Cache

D – Diretorio

Imagen de Hwang, 1993

MULTICOMPUTADORES

Es básicamente una red de computadores que se comunica por paso de mensajes, el acoplamiento es más débil que en los multiprocesadores.

NORMA – NO Remote Memory Access

21

Nodo

Imagen de Hwang, 1993

MULTICOMPUTADORES

Ventajas:

aumento del ancho de banda de la memoria

reduce latencias en el acceso a memoria

soporta mayor número de procesadores

Particularidades:

Memorias locales privadas

Comunicación mediante paso de mensajes

MPI Message Passing Interface

PVM: parallel Virtual Machine

22

MULTICOMPUTADORES

1ª generación (83-87)

Arquitectura hipercubo

Conmutación software de mensajes

CosmicCube

Intel iPSC860

2ª generación (87-92)

Arquitectura en retícula (mesh)

Enrutamiento hardware de mensajes

Parsys Supernodo 1000

Intel Paragon

3ª generación (93-…)

Un sólo chip con el procesador y comunicaciones

MIT J-Machine

Caltech Mosaic

23

SUPERCOMPUTADORES

24

(1) Computadores vectoriales

(2) Máquinas SIMD (matriciales)

Procesador escalar + procesador vectorial

Múltiples elementos de proceso bajo la supervisión de una única unidad de control

Número pequeño de procesadores potentes con hardware específico para procesamiento vectorial

Enfocadas al paralelismo masivo de datos

COMPUTADORES VECTORIALES

25

Host

computer

26

Memoria a memoria

Registro a registro

Los registros vectoriales almacenan operandos y resultados vectoriales.

CRAY-1

C-1, C-2

VP100/200

J-90

Emplean una unidad de memoria en la que almacenan los operandos y resultados vectoriales.

CDC-STAR100

TI-ASC

CYBER-205

COMPUTADORES VECTORIALES: ARQUITECTURAS

RESUMEN

27

Organizaciones de Procesadores

SISD

SIMD

MISD

MIMD

Uniprocesadores

Memoria Compartida (Fuertemente Acoplados

Procesadores Matriciales

Memoria Distribuida (Debilmente Acoplados)

Multiprocesadores Simetricos (SMP)

Clusters

Acceso No-Uniforme a Memoria (NUMA)

Procesadores Vectoriales

ENTORNOS DE PROGRAMACIÓN

28

El paralelismo debe ser soportado a nivel de:

Sistema operativo

Herramientas de programación

Los sistemas operativos paralelos deben permitir:

Planificación paralela

Asignación de recursos (memoria, periféricos…)

Comunicación

Protección de memoria y conjuntos de datos

Prevención de bloqueos

Manejo de excepciones

HERRAMIENTAS DE PROGRAMACIÓN

29

Imagen de Hwang, 1993

ARQUITECTURAS DEL PROCESADOR: EVOLUCIÓN

Chip uniprocesador

Micros convencionales

Procesadores superescalares

Procesadores superespeculativos

Procesadores multithread

Trace processors

Chip multiprocesador

Vector IRAM processors

Single-chip multiprocesors (multicore)

Raw configurable processors.

30

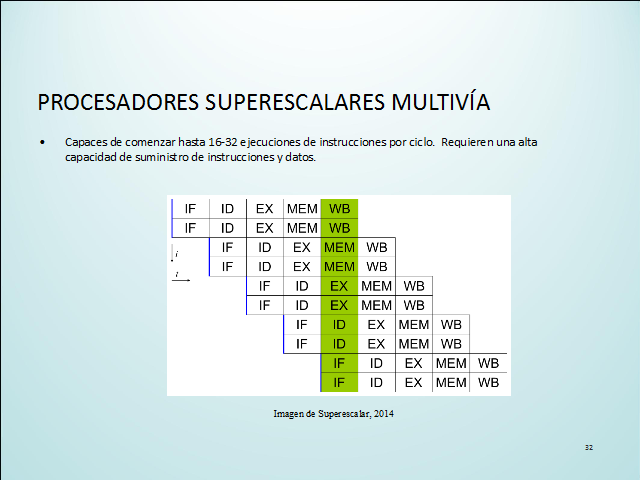

PROCESADORES SUPERESCALARES MULTIVÍA

Capaces de comenzar hasta 16-32 ejecuciones de instrucciones por ciclo. Requieren una alta capacidad de suministro de instrucciones y datos.

31

Imagen de Superescalar, 2014

ARQUITECTURAS SUPERESPECULATIVAS

La ejecución especulativa es la ejecución de código por parte del procesador que no tiene por qué ser necesaria a priori.

La ejecución especulativa no es más que una optimización. Sólo es útil cuando la ejecución previa requiere menos tiempo y espacio que el que requeriría la ejecución posterior, siendo este ahorro lo suficientemente importante como para compensar el esfuerzo gastado en caso de que el resultado de la operación nunca llegue a usarse.

Hay dos líneas:

Microarquitecturas con búsquedas de hasta 32 instr (anchura), buffer de reordenación de 128, y colas de almacenamiento de 128 entradas para varias configuraciones de memoria.

Utilización de modelos de dependencia débil para conseguir prestaciones superescalares de hasta 19 instrucciones por ciclo (IPC) puntuales y 9 IPC de media en el test SPEC-95.

32

MULTI-THREADING

El paradigma de multihilo ha llegado a ser más popular a medida que los esfuerzos para llevar más adelante el paralelismo a nivel de instrucción se han atascado desde finales de los años 1990.

Hardware Support para threads:

SuperThreading

HyperThreading

Simultaneous Multi Threading (SMT)

33

SINGLE-THREADED PROCESSOR

El procesador proporciona la ilusión de la ejecución concurrente.

Front-end: fetching/decoding/reordering.

Execution core: ejecución real.

Múltiples programas en la memoria, pero sólo uno se ejecuta en cada momento.

Time-slicing via context switching.

34

SIMPLIFIED EXAMPLE CPU

35

Front-end

Execution Core

(Back-end)

El front-end puede emitir 4 instrucciones simultáneas al execution core.

4-stage pipeline.

El execution core tiene 8 unidades funcionales.

Cada una: 6-stage pipeline.

36

El front-end está a punto de emitir 2 instrucciones.

En el ciclo siguiente se emitirán 3.

En el siguiente 1, etc.

Un hardware complejo se encarga de decidir la siguiente instrucción en ser emitida.

SIMPLIFIED EXAMPLE CPU

Front-end

Execution

Core

37

En el ciclo actual, 2 unidades funcionales están siendo usadas.

En el siguiente sólo una, etc.

Los huecos en blanco son pipeline "bubbles": oportunidades perdidas para hacer algo útil, debido a un mal paralelismo a nivel de instrucciones

SIMPLIFIED EXAMPLE CPU

Front-end

Execution

Core

BLOCK MULTI-THREADING

38

RAM

CPU

4 threads en memoria.

En la arquitectura tradicional, sólo se ejcuta el rojo.

Cuando el thread rojo se atasca o termina, se pasa a otro thread.

Coarse-grained multithreading.

Imagen de Ars Tecnica, 2002

SINGLE-THREADED SMP (SYMMETRIC MULTI-PROCESSING)

2 threads se ejecutan a la vez, pero en CPUs distintas.

Se dobla el número de burbujas.

Doble velocidad y doble gasto.

39

Imagen de Ars Tecnica, 2002

INTERLEAVED MULTI-THREADING. SUPER-THREADING

Fine-grained o time-sliced multithreading.

Principio: el procesador puede ejecutar más de un thread al mismo tiempo.

Requiere mejor hardware.

Menor gasto.

En cada etapa del front-end solo se puede ejecutar un thread.

40

Imagen de Ars Tecnica, 2002

SIMULTANEOUS MULTI-THREADING. HYPER-THREADING

Principio: el procesador puede ejecutar más de un hilo a la vez, incluso dentro del mismo ciclo de reloj!

Requiere hardware aún más complejo.

En el esquema: sólo dos threads se ejecutan simultáneamente.

Desde el punto de vista operativo, hay dos procesadores "lógicos".

41

Imagen de Ars Tecnica, 2002

TRACE (MULTISCALAR) PROCESSORS

La idea es utilizar un trace processor que consiste en múltiples cores de ejecución en un chip, cada uno de los cuales ejecuta simultáneamente una traza diferente del código.

Todos excepto uno de los cores ejecutan trazas especulativas utilizando predicción de saltos para seleccionar las trazas.

La idea es que 4 cores de procesamiento puedan ejecutar 16 o más instrucciones por ciclo si cada core ejecuta 4 instrucciones por ciclo.

42

VECTOR (IRAM) PROCESSORS

Los Intelligen Random-Access Memory processors trabajan sobre tecnologías de acceso a memoria DRAM, en la hipótesis de que el cuello de botella en el futuro estará en el sistema de memoria.

Buscan construir multiprocesadores escalables empotrados en un único chip con arrays de memoria de gran escala.

Al meter la memoria en el chip aumenta el ancho de banda de acceso a la memoria lo que permitiría un procesamiento vectorial más barato.

Para ejecutar código vectorial el código tiene que ser vectorizable.

43

SINGLE-CHIP MULTIPROCESSORS (MULTICORE)

Buscan meter en un chip entre 4 y 16 procesadores monocore avanzados.

Cada uno de los procesadores está fuertemente acoplados con una cache pequeña de 1er nivel, y todos los procesadores comparten una cache de 2º nivel.

Los procesadores pueden colaborar en tareas paralelas o ejecutar tareas independientes.

Requiere código con paralelismo explícito para aprovechar todo el potencial.

44

RAW (CONFIGURABLE) PROCESSORS

Buscan explotar el paralelismo masivo dentro del chip, con cientos de procesadores muy simples, cada uno con una cierta lógica reconfigurable.

La ejecución paralela y las comunicaciones se reordenan por software para su control y coordinación.

Esto elimina las interfaces del juego de instrucciones ya que la arquitectura es replicada directamente para su exposición al compilador.

El compilador adapta el hardware a cada aplicación.

45

Imagen de Raw Architecture Processor, 2014

[Silc, 1999] J. SILC. Processor Architecture. Springer 1999

[Hwang, 1993] K. HWANG Advanced Computer Architecture, Mc Graw-Hill, 1993

[Ars Tecnica, 2006] Peakstream article, Ars Technica, http://arstechnica.com/gadgets/2006/09/7763/

[Superescalar, 2014] http://en.wikipedia.org/wiki/Superscalar

[Ars Tecnica, 2002] Introduction to Multithreading, Superthreading and Hyperthreading, Ars Technica, http://arstechnica.com/features/2002/10/hyperthreading/

[Raw Architecture Processor, 2014] Raw Architecture Processor, http://groups.csail.mit.edu/cag/raw/

46

REFERENCIAS

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |