Introducción al diseño de sistemas digitales reconfigurables en FPGA (página 2)

LCD

El LCD es el encargado de mostrar minutos, segundos y horas por pantalla.

No todos los datos cargados en la pantalla son visibles, por esta razón será necesario tabular los datos para situarlos en la región visible.

Dentro del código original se ha incorporado un proceso de adquisición de datos provenientes de la maquina de estados.

begin process

begin

LCD_CMDS(44) <= entrada5;

LCD_CMDS(45) <= entrada6;

LCD_CMDS(47) <= entrada3;

LCD_CMDS(48) <= entrada4;

LCD_CMDS(50) <= entrada1;

LCD_CMDS(51) <= entrada2;

end process;

31

Convertidor de 4 bits a ASCII

El periférico LCD necesita los datos a representar en ASCII, pero todas las salidas de información de la maquina de estados son vectores de 4 bits.

Este componente convierte los vectores de 4 bits al formato en ASCCI necesario para el LCD.

El estado 10 (“1010”) codifica un espacio en blanco a fin de ser utilizado por el componente parpadeo.

32

Parpadeo del número seleccionado.

El parpadeo se produce haciendo oscilar el dato a modificar de su valor real a 10, que corresponde a un espacio dentro del componente convertidor de datos.

33

Esquema final completo

Este esquema interconecta todos los componentes internos y las salidas y entradas físicas de la aplicación.

34

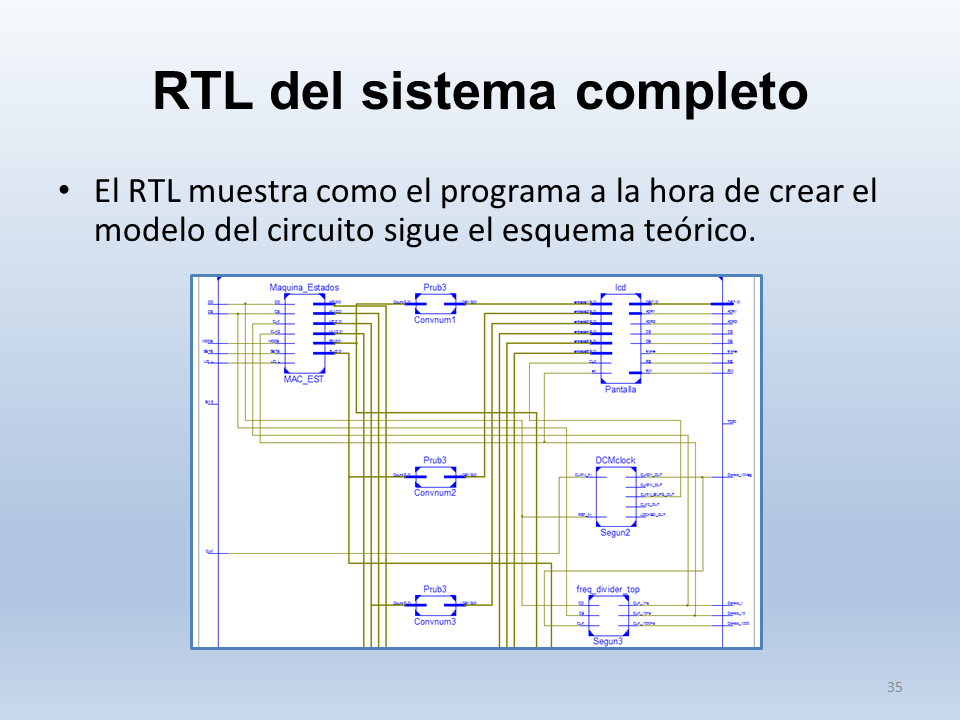

RTL del sistema completo

El RTL muestra como el programa a la hora de crear el modelo del circuito sigue el esquema teórico.

35

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |